## DM74LS952 Dual Rank 8-Bit TRI-STATE® Shift Registers

#### **General Description**

These circuits are TRI-STATE, edge-triggered, 8-bit I/O registers in parallel with 8-bit serial shift registers which are capable of operating in any of the following modes: parallel load from I/O pins to register "A", parallel transfer down from register "A" to serial shift register "B", parallel transfer up from shift register "B" to register "A", serial shift of register "B", synchronously clear. Since the registers are edgetriggered by the positive transition of the clock, the control lines which determine the mode or operation are completely independent of the logic level applied to the clock. Designed for bus-oriented systems, these circuits have their TRI-STATE inputs and outputs on the same pins.

#### **Features**

- Registers are edge-triggered by the positive transition of the clock

- All inputs are PNP transistors

- Input disable dominates over output disable

- Output high impedance state does not impede any other mode of operation

- 8-bit I/O pins are TRI-STATE buffers

- Typical shift frequency is 36 MHz

- Typical power dissipation is 305 mW

- All control inputs are active when in an "L" logic state

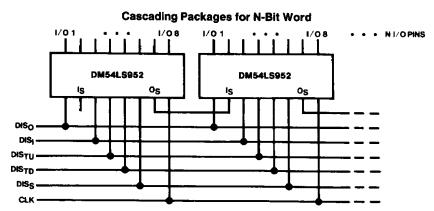

- Devices can be cascaded into N-bit word

#### Connection Diagram

#### **Dual-In-Line Package** 1/02 1/03 1/04 1/05 VCC 1/06 1/07 I/O BUFFERS CONTROL **UPPER REG "A"** LOGIC TRANSFER LOWER SHIFT REG "B" DIS<sub>0</sub> DIS DISTD CLK GND

Order Number DM74LS952N See NS Package Number N18A

**Top View**

DISS

Os

TL/F/6437-1

DISTU

#### Pin Description

DIS<sub>O</sub>—Output disable

Is-Serial input

DIS<sub>|</sub>---Input disable

DISTIL—Transfer up disable

DIS<sub>TD</sub>—Transfer down disable

DIS<sub>S</sub>-Shift disable

O<sub>S</sub>—Serial output

CLK---Clock

GND-Ground

I/O 1 . . . I/O 8-8-bit I/O pins

V<sub>CC</sub>—Supply Voltage

### **Absolute Maximum Ratings (Note)**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage 7V Input Voltage 7V

Operating Free Air Temperature Range DM74LS

0°C to +70°C

Storage Temperature Range

-65°C to +150°C

Lead Temperature (Soldering, 10 seconds)

300°C

Note: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the "Electrical Characteristics" table are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

### **Recommended Operating Conditions**

| Symbol              | Parameter                      |      | Units |      |         |  |

|---------------------|--------------------------------|------|-------|------|---------|--|

|                     |                                | Min  | Тур   | Max  | 1 Units |  |

| V <sub>CC</sub>     | Supply Voltage                 | 4.75 | 5     | 5.25 | v       |  |

| V <sub>IH</sub>     | High-Level Input Voltage       | 2    |       |      | v       |  |

| V <sub>IL</sub>     | Low-Level Input Voltage        | ,    | -     | 0.8  | v       |  |

| Гон                 | High-Level Output Current      |      |       | -5.2 | mA      |  |

| loL                 | Low-Level Output Current       |      |       | 16   | mA      |  |

| f <sub>CLOCK</sub>  | Clock Frequency (Note 5)       | 0    |       | 25   | MHz     |  |

| Clock Pulse         | High Pulse Width (Note 5)      | 25   | 17    |      | ns      |  |

|                     | Low Pulse Width (Note 5)       | 15   | 7     |      | ns      |  |

| t <sub>SET-UP</sub> | Data Set-Up Time (Note 5)      | 10   |       | -111 | ns      |  |

| <sup>t</sup> HOLD   | Data Hold Time (Note 5)        | 0    |       |      | ns      |  |

| TA                  | Free Air Operating Temperature | 0    |       | 70   | °C      |  |

# Electrical Characteristics over recommended operating free air temperature range (unless otherwise noted)

| Symbol          | Parameter                                 | Condition                                             | s (1)                                 |     | Units   |       |       |  |

|-----------------|-------------------------------------------|-------------------------------------------------------|---------------------------------------|-----|---------|-------|-------|--|

|                 |                                           |                                                       |                                       | Min | Typ (2) | Max   | Units |  |

| VI              | Input Clamp Voltage                       | $V_{CC} = Min, I_I = -18 m$                           | A                                     |     |         | - 1.5 | V     |  |

| V <sub>OH</sub> | High-Level Output Voltage                 | $V_{CC} = Min, V_{IH} = 2V,$<br>$V_{IL} = V_{IL} Max$ | I <sub>OH</sub> = -5.2 mA             | 2.4 |         |       | ٧     |  |

| V <sub>OL</sub> | Low-Level Output Voltage                  | $V_{CC} = Min, V_{1H} = 2V,$                          | I <sub>OL</sub> = 8 mA                |     | 0.25    | 0.4   | v     |  |

|                 |                                           | V <sub>IL</sub> = V <sub>IL</sub> Max                 | I <sub>OL</sub> = 16 mA               |     | 0.35    |       | \     |  |

| I <sub>I</sub>  | Input Current at Maximum<br>Input Voltage | $V_{CC} = Max, V_I = 5.5V$                            |                                       |     |         | 0.1   | mA    |  |

| I <sub>IH</sub> | High-Level Input Current                  | $V_{CC} = Max, V_1 = 2.7V$                            |                                       |     |         | 20    | μΑ    |  |

| կլ              | Low-Level Input Current                   | $V_{CC} = Max, V_I = 0.4V$                            | <del></del>                           |     |         | -50   | μА    |  |

| los             | Short-Circuit Output Current              | V <sub>CC</sub> = Max (3)                             |                                       | -20 |         | -100  | mA    |  |

| Icc             | Supply Current                            | V <sub>CC</sub> = Max (4)                             | · · · · · · · · · · · · · · · · · · · |     | 61      | 99    | mA    |  |

| OFF             | TRI-STATE I/O Current                     | V <sub>CC</sub> = Max, V <sub>IH</sub> = 2V           |                                       | 1   | 20      | μА    |       |  |

|                 |                                           |                                                       | $V_{O} = 0.4V$                        |     |         | -20   | μА    |  |

Note 1: For conditions shown as min or max, use the appropriate value specified under recommended operating conditions.

Note 2: All typical values are at  $V_{CC} = 5V$ ,  $T_A = 25$ °C.

Note 3: Not more than one output should be shorted at a time, and the duration of the short circuit should not exceed one second.

Note 4: ICC is measured with serial output open, the clock and shift disable input at 2.4V. All other control inputs and I/O pins grounded.

Note 5:  $T_A = 25^{\circ}C$  and  $V_{CC} = 5V$ .

| Symbol               | Parameter                                                           | Conditions                                         | Min | Max | Units |  |

|----------------------|---------------------------------------------------------------------|----------------------------------------------------|-----|-----|-------|--|

| f <sub>MAX</sub>     | Maximum Clock Frequency                                             |                                                    | 25  |     | MHz   |  |

| <sup>t</sup> PLH     | Propagation Delay Time, Low-to-High-Level from Clock to Any Outputs |                                                    | 7   | 33  | ns    |  |

| t <sub>PHL</sub>     | Propagation Delay Time, High-to-Low Level from Clock to Any Output  | $C_{L} = 15  \text{pF, R}_{L} = 1  \text{k}\Omega$ | 10  | 48  | ns    |  |

| <sup>t</sup> ENABLE  | Enable Time from Any Control Inputs                                 |                                                    | 5   | 24  | ns    |  |

| <sup>†</sup> DISABLE | Disable Time from Any Control Inputs                                |                                                    | 6   | 27  | ns    |  |

| t <sub>PZH</sub>     | Output Enable Time to High Level                                    |                                                    | 5   | 23  | ns    |  |

| t <sub>PZL</sub>     | Output Enable to Low Level                                          |                                                    | 4   | 18  | ns    |  |

| t <sub>PHZ</sub>     | Output Disable Time from High Level                                 | $C_L = 5  pF, R_L = 1  k\Omega$                    | 5   | 23  | ns    |  |

| tpLZ                 | Output Disable Time from Low Level                                  | οι ορι,τι <u>ι πταν</u>                            | 6   | 27  | ns    |  |

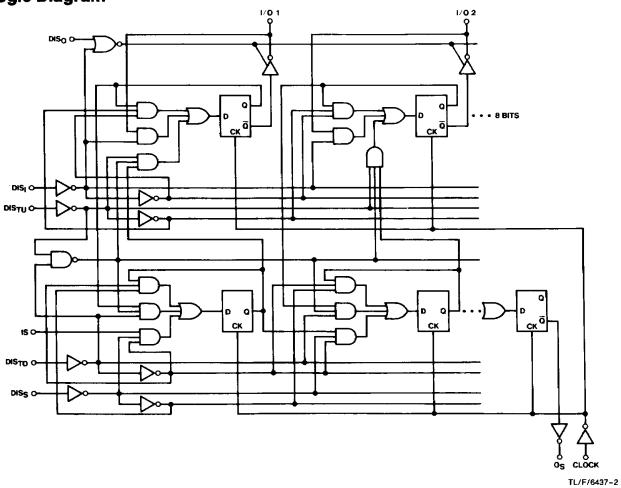

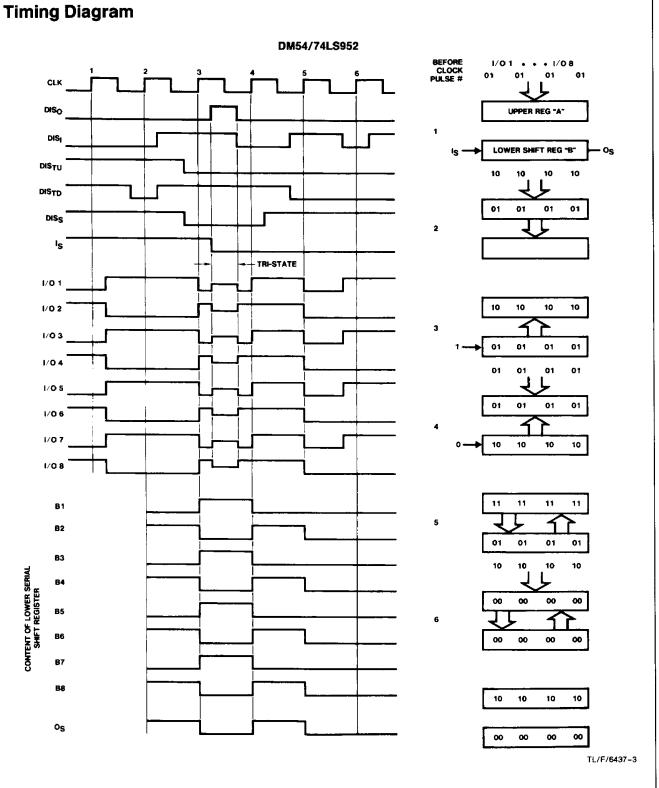

# **Logic Diagram**

| ø           |

|-------------|

| Ť           |

| 2           |

| ୍ଦ          |

| <b>-</b>    |

| $\subseteq$ |

| 0           |

| ≔           |

| Ü           |

| _           |

| 3           |

|             |

Table i

|  |                                        |                                                                           |                     |                     |                                    | ,,,,,               | < .                                     | B                                                               |                     | n<br>G                                 |                                 | ars to                                    |                     |                                       |                     |                                     |                                   |                     |                               |                                                                 |             |

|--|----------------------------------------|---------------------------------------------------------------------------|---------------------|---------------------|------------------------------------|---------------------|-----------------------------------------|-----------------------------------------------------------------|---------------------|----------------------------------------|---------------------------------|-------------------------------------------|---------------------|---------------------------------------|---------------------|-------------------------------------|-----------------------------------|---------------------|-------------------------------|-----------------------------------------------------------------|-------------|

|  | Os                                     |                                                                           | 71770               | Stable state        | Entering data from I/O to reg. "A" |                     | ransier data up irom reg. B. to reg. A. | Reg. "A" will OR data from I/O to reg. "B"                      | T ( 1 ( 1 ) )       | Iransiei data down nomi reg. A to reg. | Entering data and transfer down | (1) Synchronously clear both registers to | (2) logic "L" level | (3) Enter data to reg. "A" clear reg. | ((U))               | Serial stiffing in the lower reg. B | Entering data and serial shifting |                     | ransier up and senai smilling | DOR function and serial shifting                                |             |

|  |                                        |                                                                           | 28 28 28            |                     | <b>P8</b>                          | 8 8 8               |                                         | 88                                                              | 88                  | <b>a</b> 8                             |                                 |                                           | ٦                   | 7q<br>7d<br>57                        |                     | p7                                  | b7<br>b7                          |                     | 29                            |                                                                 |             |

|  |                                        | B8                                                                        | <b>8</b> 9          | 80                  | <b>P8</b>                          | 8q                  | <b>9</b> 8                              | 82                                                              | 88<br>8             | a8                                     | <b>a8</b>                       | ٦                                         | _                   | ٦                                     | <b>2</b> q          | <b>P</b> 2                          | p2                                | p2                  | <b>P</b> 2                    | <b>P</b> 2                                                      |             |

|  | g. "B"                                 | 87                                                                        | P7                  | <b>b7</b>           | <b>p</b> 2                         | P2                  | <b>P</b> 2                              | P2                                                              | a7                  | a7                                     | a7                              | ٦                                         | _                   | ٦                                     | 9q                  | 99                                  | 99                                | 99                  | <b>9</b> 9                    | 99                                                              |             |

|  | hift Re                                | B6                                                                        | 9q                  | 90                  | 9q                                 | 99                  | 9q                                      | 9q                                                              | ae                  | a6                                     | ae                              | ٦                                         | _                   | ٦                                     | <b>P</b> 2          | p2                                  | p2                                | <b>p</b> 2          | <b>p</b> 2                    | 52                                                              |             |

|  | Content of Lower Serial Shift Reg. "B" | BS                                                                        | 9 <b>9</b>          | <b>p</b> 2          | p2                                 | p2                  | <b>p</b> 2                              | p2                                                              | аŞ                  | a5                                     | а5                              | _                                         | _                   | ٦                                     | 4                   | 7                                   | <b>p4</b>                         | <b>5</b> 4          | <b>p</b>                      | 7                                                               |             |

|  | Lower                                  | B4                                                                        | <b>b4</b>           | 4                   | 4                                  | ¥                   | 7                                       | 4                                                               | a4                  | 84                                     | <b>a4</b>                       |                                           | _                   | _                                     | <b>63</b>           | ည                                   | <b>p</b> 3                        | 6q                  | 63                            | <b>63</b>                                                       |             |

|  | ent of                                 | <b>B</b> 3                                                                | P3                  | <b>6</b> 3          | <b>p</b> 3                         | p3                  | <b>6</b> 3                              | ည                                                               | <b>a</b> 3          | <b>a</b> 3                             | a3                              | _                                         | _                   | 7                                     | <b>P</b> 2          | <b>p</b> 5                          | p5                                | p2                  | <b>P</b> 2                    | p5                                                              |             |

|  | Cont                                   | B2                                                                        | p2                  | p2                  | p5                                 | p2                  | <b>P</b> 5                              | p5                                                              | a2                  | a2                                     | a2                              | _                                         | _                   | _                                     | 2                   | 5                                   | p1                                | 5                   | 5                             | <b>P</b> 4                                                      |             |

|  |                                        | B1                                                                        | 2                   | 5                   | þ                                  | b1                  | 5                                       | p1                                                              | a1                  | a1                                     | a1                              | _                                         | _                   | _                                     | ס                   | ס                                   | ъ                                 | ъ                   | v                             | ס                                                               |             |

|  | Content of Upper Reg. "A"              | 2 A3 A4 A5 A6 A7 A8                                                       | 2 a3 a4 a5 a6 a7 a8 | 2 a3 a4 a5 a6 a7 a8 | 9 14 15 16 17 19                   | 2 b3 b4 b5 b6 b7 b8 | 2 b3 b4 b5 b6 b7 b8                     | $\leftarrow \leftarrow DOR \rightarrow \rightarrow \rightarrow$ | 2 a3 a4 a5 a6 a7 a8 | 2 a3 a4 a5 a6 a7 a8                    | 13 14 15 16 17 18               | ווווו                                     | 1 1 1 1 1 .         | 1 13 14 15 16 17 18                   | 2 a3 a4 a5 a6 a7 a8 | 2 a3 a4 a5 a6 a7 a8                 | 13 14 15 16 17 18                 | 2 b3 b4 b5 b6 b7 b8 | 2 b3 b4 b5 b6 b7 b8           | $\leftarrow \leftarrow DOR \rightarrow \rightarrow \rightarrow$ |             |

|  | ខិ                                     | A1 A2                                                                     | a1 a2               | a1 a2               | 1 12                               | b1 b2               | b1 b2                                   | ↓                                                               | a1 a2               | a1 a2                                  | 11 12                           | ר                                         |                     | 1 12                                  | a1 a2               | a1 a2                               | 14                                | b1 b2               | b1 b2                         | ↓                                                               |             |

|  | 8-Bit 1/0<br>Pins                      |                                                                           | Hi-Z                | Output              | Input                              | Z-iH                | Output                                  | Input                                                           | Z-!H                | Output                                 | Input                           | Hi-Z                                      | Output              | Input                                 | Hi-Z                | Output                              | Input                             | Hi-Z                | Output                        | Input                                                           |             |

|  |                                        |                                                                           |                     | ×                   | ×                                  | ×                   | ×                                       | ×                                                               | ×                   | ×                                      | ×                               | ×                                         | ×                   | ×                                     | ъ                   | þ                                   | D                                 | P                   | Р                             | d                                                               |             |

|  | S CLI                                  |                                                                           | ×                   | ×                   | <b>←</b>                           | <b>←</b>            | <u>←</u>                                | <b>←</b>                                                        | <b>←</b>            | <b>←</b>                               | <b>←</b>                        | <u>←</u>                                  | <b>←</b>            | <b>←</b>                              | <del></del>         | <b>←</b>                            | ←                                 | <b>←</b>            | <u>←</u>                      | <b>—</b>                                                        |             |

|  | DIS.                                   | DIS <sub>O</sub> DIS <sub>TU</sub> DIS <sub>TU</sub> DIS <sub>S</sub> CLK |                     | <u> </u>            | Ξ                                  | <u> </u>            | <u> </u>                                | _                                                               | ×                   | ×                                      | ×                               | ×                                         | ×                   | ×                                     | بـ                  | _                                   | _                                 |                     |                               |                                                                 |             |

|  | 50                                     |                                                                           | <u> </u>            | I                   | I                                  | <b>I</b>            | I                                       | Ξ                                                               | _                   |                                        |                                 |                                           | _                   | _                                     | I                   | I                                   | I                                 | Ξ                   | Ι                             | Ξ                                                               |             |

|  | DIST                                   |                                                                           | <b>I</b>            | I                   | I                                  | _                   | _                                       | _                                                               | I                   | I                                      | Ξ                               |                                           | _                   | _                                     | I                   | I                                   | Ξ                                 | _                   | _                             | _                                                               |             |

|  | 5                                      |                                                                           | I                   | I                   |                                    | I                   | I                                       | _                                                               | I                   | I                                      | _                               | Ξ                                         | I                   |                                       | Ŧ                   | I                                   | _                                 | Ι                   | Ξ                             | _                                                               | - Dog't Car |

|  | Sig                                    |                                                                           | I                   | _                   | ×                                  | I                   | ب                                       | ×                                                               | I                   | بـ                                     | ×                               | I                                         | _                   | ×                                     | Ι                   | ١                                   | ×                                 | I                   | _                             | ×                                                               | >           |

$X \equiv Don't Care$

Hi-Z/Output/Input/ ≡ High impedance state/output state/input state at ... a8/b1 ... b8 ≡ The content of the upper register "A"/the lower serial shift register "B" before the most recent ↑ transition of the clock

$I_1 \dots I_9 \equiv \text{The level of steady state inputs of the I/O pins}$  DOR  $\equiv$  "Data ORing function" ORing data from both I/O pins and register "B", i.e.,  $I_1 + b1$ ,  $I_2 + b2$ ,  $I_3 + b3 \dots I_8 + b8$

$d \equiv Data of the serial input$

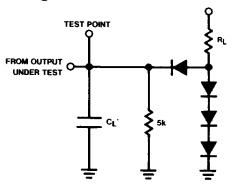

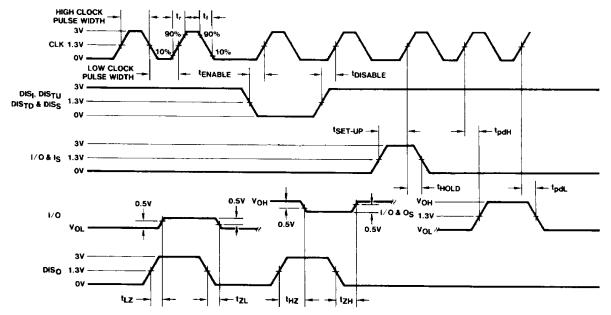

### **AC Test Circuit and Switching Time Waveforms**

All diodes are 1N916 or 1N3064.

C<sub>L</sub> includes probe and jig capacitance.

TL/F/6437-4

TL/F/6437-5

All input pulses are supplied by generators having t\_r  $\leq$  15 ns, t\_f  $\leq$  6 ns, PRR  $\leq$  1 MHz,  $Z_{OUT} \approx 50\Omega$ .

# **Cascading Packages**

TL/F/6437-6

### This datasheet has been downloaded from:

www. Data sheet Catalog.com

Datasheets for electronic components.

# National Semiconductor was acquired by Texas Instruments.

http://www.ti.com/corp/docs/investor\_relations/pr\_09\_23\_2011\_national\_semiconductor.html

This file is the datasheet for the following electronic components:

DM74LS952N - http://www.ti.com/product/dm74ls952n?HQS=TI-null-null-dscatalog-df-pf-null-wwe